Project introduction: Digital Filter Blocks in MyHDL and their integration in pyFDA

Hi everyone! After a lot of hesitation and several failed attempts, I have finally entered the world of blogging. A little about myself : My name is Sriyash Caculo and I’m a third year undergrad student at BITS Pilani K.K. Birla Goa Campus pursuing a major in Electronics and Instrumentation engineering. Being an electronics engineer, I developed an interest in Digital Signal Processing and its implementation on hardware.

This blog-post is the first of many to come for the next few months as I have been selected to work under 'Free and Open Source Silicon Foundation' (FOSSi Foundation) for Google Summer of Code ’ 18.

What is Google Summer of Code (GSoC) ?

Excerpt from the GSoC website:

Google Summer of Code is a global program focused on introducing students to open source software development. Students work on a 3 month programming project with an open source organisation during their break from university.

As a part of Google Summer of Code, student participants are paired with a mentor from the participating organisations, gaining exposure to real-world software development and techniques. Students have the opportunity to spend the break between their school semesters earning a stipend while working in areas related to their interests. Most importantly, more code is created and released for the use and benefit of all.

What my project is all about?

My project titled “Digital Filter Blocks in MyHDL and PyFDA integration" aims to leverage and demonstrate the advantages of MyHDL, PyFDA and python in general in the field of Digital Filter design. MyHDL is a Python module for developing and testing HDL code. PyFDA is a GUI based tool in written in Python/Qt for analysing and designing discrete time filters. Algorithm exploration, modelling, designing and simulating of digital filters can all be done in Python and PyFDA. It is important to note here that PyFDA operates with floating point arithmetic as opposed to the implementable fixed point arithmetic in MyHDL.

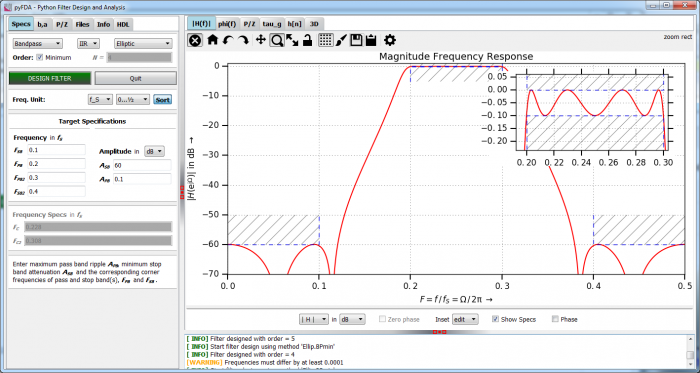

Screenshot of current version of PyFDA

Why MyHDL?

Digital filter design and implementation in hardware usually is a two stage process, algorithm development in a language like Python, Matlab or Java and RTL design in a Hardware Description Language like VHDL or Verilog. This requires going back and forth between the two environments multiple times to check if the hardware design is consistent with the required specifications. When I came across MyHDL, the idea of developing the algorithm and RTL design in the same Python environment really excited me. Another aspect of MyHDL is that designs can be automatically converted to equivalent code in both Verilog and VHDL making language neutral designs possible.

Why PyFDA?

Further, linking MyHDL and PyFDA has more benefits. This combination could fill a gap in the open source tool chain between algorithm development and HDL fixpoint blocks which would eliminate the need for commercially licensed tools like Mathworks hdl-coder.

After the completion of the project, the following design flow would be operational: First, PyFDA determines filter coefficients and poles/zeros from design specifications and verifies the filter response in time and frequency domain. This will help find errors in design quickly. PyFDA automatically converts filter coefficients from floating point to fixed point and passes these to the MyHDL filter blocks which generate HDL code, either VHDL or Verilog. The HDL results will match the results acquired in PyFDA and MyHDL filter blocks will take care of all the hardware requirements/details.

These are the main milestones that the project hopes to complete:

- Robust and rigorously tested implementation of multiple Digital Filter Blocks in MyHDL:

- Direct form FIR filter.

- Systolic implementation of linear phase FIR filter.

- Parallel path implementation of IIR filter.

- Tests for filter blocks to check correctness & performance.

- Integration of the filters with PyFDA which would involve design of a suitable interface to pass filter coefficients to MyHDL filter blocks.

- Tutorials and Documentation for all filter modules to improve usability.

Lastly, I’m happy to have Christopher Felton and Christian Muenker as my mentors for this project. Every blogger I suppose, hopes that every reader of his or her work could benefit from having read it. My hope is that over the next couple of months if nothing else, readers appreciate the growing open source community in the field of Digital Signal Processing and hardware design and perhaps foray into these domains themselves! Looking forward to a productive summer ahead!

- Comments

- Write a Comment Select to add a comment

Sriyash,

Welcome! I was a GSOC mentor several years ago, and I really enjoyed seeing the amazing work that was produced. In just a few months, they had some amazing implementations.

I'm looking forward to following your work. Writing about your GSOC project should be a great way to contribute on lots of different levels inside and outside the GSOC program. If there is anything I can do to help, feel free to ask.

David,

Thank you for your kind words! I will make sure to post regular updates and keep the blog updated with my progress. Thanks again!

Hi Sriyash. I look forward to your next blog. (I hope I'm able to understand it.) I have a favor to ask of you: Just before you post your next blog will you please go through your blog's text and clearly define all the acronyms contained in your next blog? That will help folks (including myself) who are not so familiar with the various acronyms you used in your above blog.

Thanks Sriyash.

Hello Rick,

I apologise for the slightly late response, I somehow missed to see this comment. I will definitely keep that in mind before my next post. I'm also more than happy to clarify things in the comments if need be. Thank you for the feedback!

To post reply to a comment, click on the 'reply' button attached to each comment. To post a new comment (not a reply to a comment) check out the 'Write a Comment' tab at the top of the comments.

Please login (on the right) if you already have an account on this platform.

Otherwise, please use this form to register (free) an join one of the largest online community for Electrical/Embedded/DSP/FPGA/ML engineers: