FPGA IIR Lowpass Direct Form I Filter Generator

This code snippet illustrates how to use the SIIR object to genrate Verilog and VHDL for a Direct Form I IIR Lowpass filter. More information available from this blog post and code for the SIIR object is available here.

To use the generator download and install the dependencies, download the Python script, and either modify the script (bottom, main script execution) or execute the commands in the code snippet section.

Dependencies:

* siir object (above link)

* python 2.7 (tested with 2.7)

* numpy (numpy.scipy.org)

* scipy (www.scipy.org)

* MyHDL (www.myhdl.org)

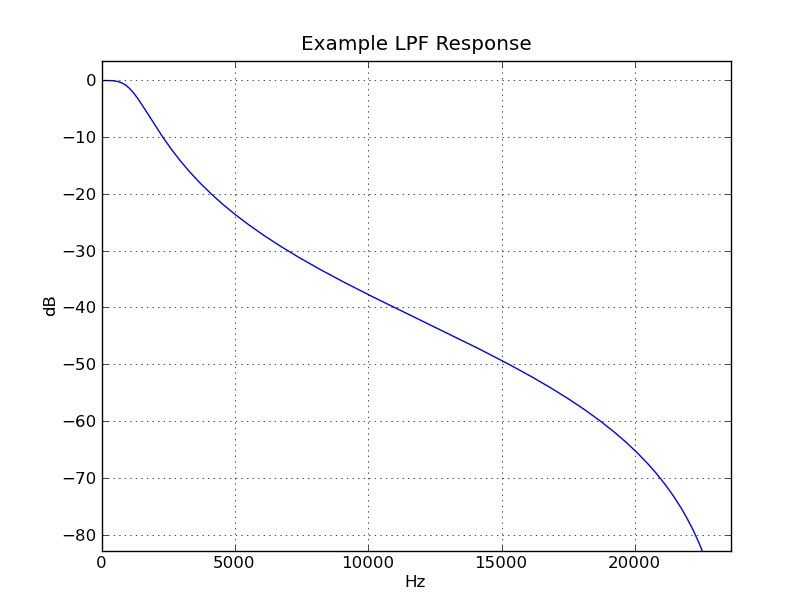

Example Plots Generated; the designed filter response.

The simulated filter response.

After running the Convert method the Verilog and VHDL will be generated. The Verilog or VHDL can then be used in normal FPGA process.

# Instantiate the SIIR object. Pass the cutoff frequency

# Fc and the sample rate Fs in Hz. Also define the input

# and output fixed-point type. W=(wl, iwl) where

# wl = word-length and iwl = integer word-length. This

# example uses 23 fraction bits and 1 sign bit.

>>> from siir import SIIR

>>> flt = SIIR(Fstop=1333, Fs=48000, W=(24,0))

# Plot the response of the fixed-point coefficients

>>> plot(flt.hz, 20*log10(flt.h)

# Create a testbench and run a simulation

# (get the simulated response)

>>> from myhdl import Simulation

>>> tb = flt.TestFreqResponse(Nloops=128, Nfft=1024)

>>> Simulation(tb).run()

>>> flt.PlotResponse()

# Happy with results generate the Verilog and VHDL

>>> flt.Convert()