I don’t often convert VHDL to Verilog but when I do ...

VHDL to Verilog

I don’t often convert VHDL to Verilog but when I do it is not the most exciting task in the world (that is an understatement). For the most part I am HDL agnostic. Well that is not true, I have a strong preference for MyHDL, and an insubstantial preference for VHDL over Verilog. The choice of HDL for a project is often complicated, irrational, sometimes rational, but most often random. It is often not a choice of the developer - for whatever reason. In the end “you get what you get and don’t throw a fit”.

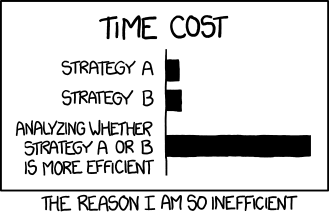

(comic source XKCD)

For open-source projects, especially if they have mixed source, I need to convert to a single HDL: Verilog or VHDL (of course assuming I can’t use MyHDL). The logical choice here, for an open-source project, is Verilog because the highest quality FOSS HDL simulator is Icarus Verilog [1] (iverilog).

Although GHDL is a great FOSS VHDL simulator, it is lacking [3] and the foreign language interface is insufficient (lacks a complete VHPI). The referenced articles are more than a couple years old and GHDL is still being actively developed. Even though there have been improvements and features added, I believe GHDL is still lacking (e.g. complete VHPI).

When I need to convert from VHDL to Verilog I use vhd2vl [4]. This tool is not a magic bullet. It will fail for most VHDL modules out there, but it can be used to do much of the heavy lifting. The process is to run the source through the tool, when it barfs, interrogate the offending line(s). Then, either comment out the line (leaving a comment to come back and manually fix) or change the failing code in VHDL. I have mainly used the first option because it is annoying to change the code and still have it fail. After the failing code is commented, repeat until the module converts without error. At this point you need to go back and fix all the failed conversions. The failed conversion are typically straightforward to fix.

The following is a list of VHDL features the tool does not support:

- arrays (for the most part these are easy to fix post conversion).

- entity instantiation (these seems odd, seems like I must be missing something).

- package and records.

The above are straightforward to manually convert (often easy to fix without knowing the context) but for a large project it can take substantial time. I have found the most time consuming to fix are arrays and records passed through ports.

Using vhd2vl

The vhd2vl tool can be downloaded from [4]. The tool is distributed as source and needs to be compiled. On Linux (Unix) systems this is straightforward (if you flex or bison).

Example(s)

Example 1

As an example, take this memory test component in the Xess VHDL library. Let's pass it to the tool and see what happens.

>> vhd2vl MemTest.vhdThe first error (well it didn’t take long for it to fail):

syntax error, unexpected NAME, expecting ENTITY or ARCHITECTURE at "package" in line 29.

As the above suggests, comment out the offending line and make a note to come back and manually fix. After a couple iterations of running the tool and commenting, the file converts. Then the manual conversion in the Verilog file needs to be completed. After the manual conversion, the Verilog file compiles and is valid (well we don’t know if it is valid until we test it).

The commented VHDL and the converted and modified Verilog for this example can be found here.

Full Core Conversion

I have converted an open-cores JPEG encoder from VHDL to Verilog [5] and used the above process. I do have the problem of verifying the conversion - right now this is simply accomplished if the encoder works in the system (simulation test environment). I don’t have a formal method to compare the conversion but the Python test enviroment provides a nice verification enviroment.

Verilog to VHDL

Converting Verilog to VHDL is a little easier, Icarus Verilog supports a “VHDL” target. Since Icarus is a full Verilog parser it doesn’t (at least not as much) suffer from the limitations as vhd2vl. But I have not tried it as I have had no need to convert in the other directions.

Conclusion

Given the tools I have been able to find, conversion from VHDL to Verilog is possible but is still a lot of manual effort. As stated, the main reason to convert is not to have Verilog source but to use FOSS tools for open-source projects. The Icarus Verilog simulator appears to be the highest quality simulator available and no FOSS tools support mixed source (best of my knowledge).

Again note, from my perspective this is only useful if there is a limitation in a toolflow and having a single HDL source is beneficial, as described above. The converted code, more than likely, will be limited in some aspect and the conversion requires considerable effort.

In addition to Icarus Verilog, the Verilator [6] simulator also seems to be a high quality FOSS tool. The recently released Tachyon's CVC Verilog simulator is another FOSS opiton. CVC is the fastest Verilog simulator available (free or commercial). There are many high quality Verilog simulators available to use whereas there is only one VHDL simulator.

If there are better tools or other options for converting VHDL to Verilog please leave a comment with links and/or describing the tool/flow.

Resources (Links)

[1] http://iverilog.icarus.com/

[2] http://www.sigasi.com/content/lacking-open-source-vhdl-simulator

[3] http://www.sigasi.com/content/why-ghdl-currently-not-good-enough

[4] http://doolittle.icarus.com/~larry/vhd2vl/

- Comments

- Write a Comment Select to add a comment

Hi Yann,

Do you have a link for vasy tools ?

Thanks.

Martoni

To post reply to a comment, click on the 'reply' button attached to each comment. To post a new comment (not a reply to a comment) check out the 'Write a Comment' tab at the top of the comments.

Please login (on the right) if you already have an account on this platform.

Otherwise, please use this form to register (free) an join one of the largest online community for Electrical/Embedded/DSP/FPGA/ML engineers: