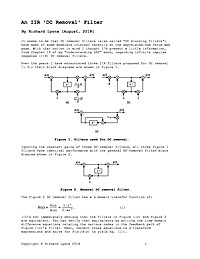

An IIR 'DC Removal' Filter

It seems to me that DC removal filters (also called "DC blocking filters") have been of some moderate interest recently on the dsprelated.com Forum web page. With that notion in mind I thought I'd post a little information, from Chapter 13 of my "Understanding DSP" book, regarding infinite impulse response (IIR) DC removal filters.

Project Report : Digital Filter Blocks in MyHDL and their integration in pyFDA

The Google Summer of Code 2018 is now in its final stages, and I’d like to take a moment to look back at what goals were accomplished, what remains to be completed and what I have learnt. The project overview was discussed in the previous blog...

Linear Feedback Shift Registers for the Uninitiated, Part XVI: Reed-Solomon Error Correction

Last time, we talked about error correction and detection, covering some basics like Hamming distance, CRCs, and Hamming codes. If you are new to this topic, I would strongly suggest going back to read that article before this one. This time we...

Digital PLL’s, Part 3 – Phase Lock an NCO to an External Clock

Sometimes you may need to phase-lock a numerically controlled oscillator (NCO) to an external clock that is not related to the system clocks of your ASIC or FPGA. This situation is shown in Figure 1. Assuming your system has an...

Two Easy Ways To Test Multistage CIC Decimation Filters

This article presents two very easy ways to test the performance of multistage cascaded integrator-comb (CIC) decimation filters. Anyone implementing CIC filters should take note of the following proposed CIC filter test methods.

ADC Clock Jitter Model, Part 2 – Random Jitter

In Part 1, I presented a Matlab function to model an ADC with jitter on the sample clock, and applied it to examples with deterministic jitter. Now we’ll investigate an ADC with random clock jitter, by using a filtered or unfiltered...

ADC Clock Jitter Model, Part 1 – Deterministic Jitter

Analog to digital converters (ADC’s) have several imperfections that affect communications signals, including thermal noise, differential nonlinearity, and sample clock jitter [1, 2]. As shown in Figure 1, the ADC has a sample/hold...

FFT Interpolation Based on FFT Samples: A Detective Story With a Surprise Ending

This blog presents several interesting things I recently learned regarding the estimation of a spectral value located at a frequency lying between previously computed FFT spectral samples. My curiosity about this FFT interpolation process was triggered by reading a spectrum analysis paper written by three astronomers.

Phase or Frequency Shifter Using a Hilbert Transformer

In this article, we'll describe how to use a Hilbert transformer to make a phase shifter or frequency shifter. In either case, the input is a real signal and the output is a real signal. We'll use some simple Matlab code to simulate these systems. After that, we'll go into a little more detail on Hilbert transformer theory and design.

An Efficient Linear Interpolation Scheme

This article presents a computationally-efficient linear interpolation trick that requires at most one multiply per output sample.

Pulse Shaping in Single-Carrier Communication Systems

Some common conceptual hurdles for beginning communications engineers have to do with "Pulse Shaping" or the closely-related, even synonymous, topics of "matched filtering", "Nyquist filtering", "Nyquist pulse", "pulse filtering", "spectral...

A Differentiator With a Difference

Some time ago I was studying various digital differentiating networks, i.e., networks that approximate the process of taking the derivative of a discrete time-domain sequence. By "studying" I mean that I was experimenting with various...

Four Ways to Compute an Inverse FFT Using the Forward FFT Algorithm

If you need to compute inverse fast Fourier transforms (inverse FFTs) but you only have forward FFT software (or forward FFT FPGA cores) available to you, below are four ways to solve your problem. Preliminaries To define what we're...

Margin Call: Fermi Problems, Highway Horrors, Black Swans, and Why You Should Worry About When You Should Worry

A DSP Quiz Question

Here's a DSP Quiz Question that I hope you find mildly interestingBACKGROUNDDue to the periodic natures an N-point discrete Fourier transform (DFT) sequence and that sequence’s inverse DFT, it is occasionally reasonable to graphically plot...

Third-Order Distortion of a Digitally-Modulated Signal

Analog designers are always harping about amplifier third-order distortion. Why? In this article, we'll look at why third-order distortion is important, and simulate a QAM signal with third order distortion.

A Two Bin Exact Frequency Formula for a Pure Complex Tone in a DFT

Introduction This is an article to hopefully give a better understanding to the Discrete Fourier Transform (DFT) by deriving an exact formula for the frequency of a complex tone in a DFT. It is basically a parallel treatment to the real case...

Multi-Decimation Stage Filtering: Design and Optimization

During my research on digital FIR decimation filters I have been developing various Matlab scripts and functions. In which I have decided later on to consolidate it in a form of a toolbox. I have developed this toolbox to assist and...

Generating pink noise

In one of his most famous columns for Scientific American, Martin Gardner wrote about pink noise and its relation to fractal music. The article was based on a 1978 paper by Voss and Clarke, which presents, among other things, a simple...

Free DSP Books on the Internet

While surfing the "net" I have occasionally encountered signal processing books whose chapters could be downloaded to my computer. I started keeping a list of those books and, over the years, that list has grown to over forty books. Perhaps the...